- 您现在的位置:买卖IC网 > Sheet目录369 > W9816G6IH-6I (Winbond Electronics)IC SDRAM 16MBIT 50TSOPII

�� �

�

�

�W9816G6IH�

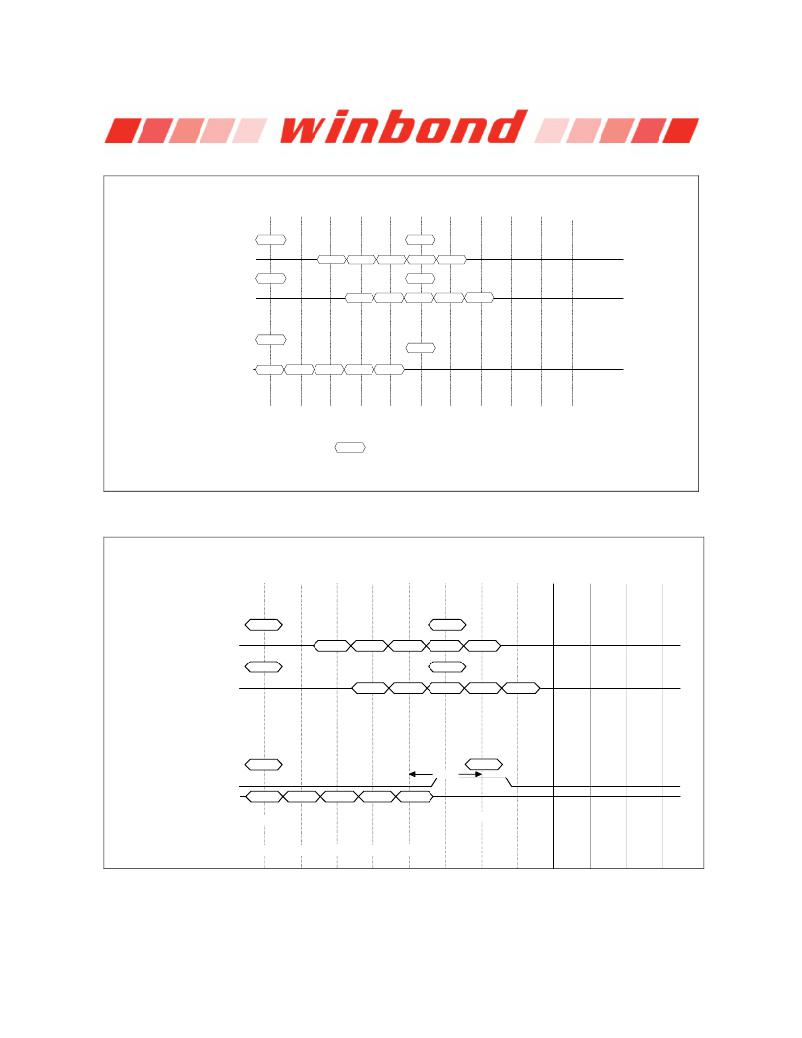

�11.19� Timing� Chart� of� Burst� Stop� Cycle� (Burst� Stop� Command)�

�0�

�1�

�2�

�3�

�4�

�5�

�6�

�7�

�8�

�9�

�10�

�11�

�(1)� Read� cycle�

�(� a� )� CAS� latency� =2�

�Command�

�Read�

�BST�

�DQ�

�Q0�

�Q1�

�Q2�

�Q3�

�Q4�

�(� b� )CAS� latency� =� 3�

�Command�

�Read�

�BST�

�DQ�

�Q0�

�Q1�

�Q2�

�Q3�

�Q4�

�(2)� Write� cycle�

�Command�

�Write�

�BST�

�DQ�

�Q0�

�Q1�

�Q2�

�Q3�

�Q4�

�Note:�

�BST�

�represents� the� Burst� stop� command�

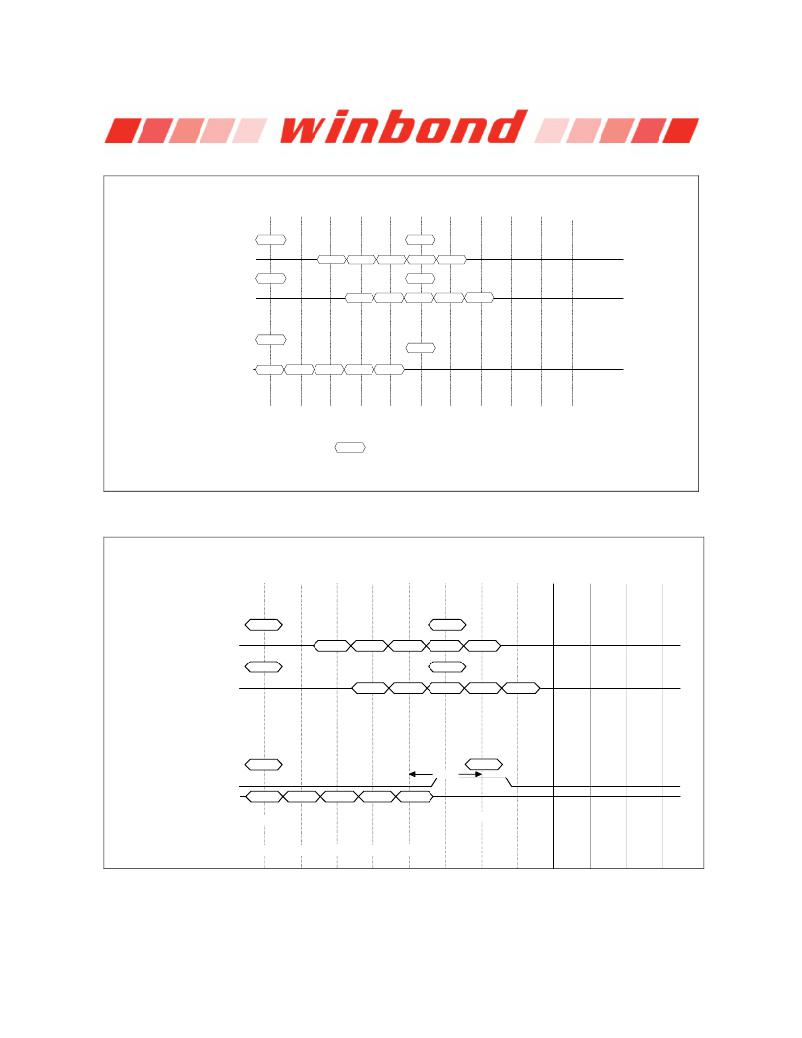

�11.20� Timing� Chart� of� Burst� Stop� Cycle� (Precharge� Command)�

�0�

�1�

�2�

�3�

�4�

�5�

�6�

�7�

�8�

�9�

�10�

�11�

�(1� )� R� e� a� d� c� y� c� le�

�(a� )� C� A� S� la� te� n� c� y� =� 2�

�C� om� m� and�

�Read�

�PRCG�

�DQ�

�Q0�

�Q1�

�Q2�

�Q3�

�Q4�

�(b� )� C� A� S� la� te� n� c� y� =� 3�

�C� om� m� and�

�Read�

�PRCG�

�DQ�

�Q0�

�Q1�

�Q2�

�Q3�

�Q4�

�(2� )� W� r� ite� c� y� c� le�

�C� om� m� and�

�W� rite�

�tW� R�

�PRCG�

�DQM�

�DQ�

�Q0�

�Q1�

�Q2�

�Q3�

�Q4�

�Publication� Release� Date:� Mar.� 22,� 2010�

�-� 38� -�

�Revision� A02�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

W9825G6JH-6I

IC SDRAM 256MBIT 54TSOPII

W9864G6JH-6I

IC SDRAM 64MBIT 54TSOPII

WM-5614

CABINET WALL MOUNT 37.25X17.9"

WRR-2244

RACK WALL MOUNT RELAY 42" X 19"

WRR-2264

RACK WALL MOUNT 75.25" X 19"

X28C512JIZ-12

IC EEPROM 512KBIT 120NS 32PLCC

X28HC256SIZ-90

IC EEPROM 256KBIT 90NS 28SOIC

X28HC64JIZ-90

IC EEPROM 64KBIT 90NS 32PLCC

相关代理商/技术参数

W9816G6IH-7

制造商:WINBOND 制造商全称:Winbond 功能描述:512K 】 2 BANKS 】 16 BITS SDRAM

W9816G6IH-7I

制造商:WINBOND 制造商全称:Winbond 功能描述:512K 】 2 BANKS 】 16 BITS SDRAM

W982504AH-7

制造商:未知厂家 制造商全称:未知厂家 功能描述:x4 SDRAM

W982504AH-75

制造商:未知厂家 制造商全称:未知厂家 功能描述:x4 SDRAM

W982504AH-8H

制造商:未知厂家 制造商全称:未知厂家 功能描述:x4 SDRAM

W982508AH

制造商:WINBOND 制造商全称:Winbond 功能描述:8M X 4 BANKS X 8 BIT SDRAM

W982508AH-7

制造商:未知厂家 制造商全称:未知厂家 功能描述:x8 SDRAM

W982508AH-75

制造商:未知厂家 制造商全称:未知厂家 功能描述:x8 SDRAM